Here I explain the KOH simulator software (ACES) from University of Chicago [1] for a chain process of DRIE followed by KOH undercut. This software is very simple yet power to understand how Si etching works and design the mask to optimize the etch speed and crystal planes [2].

Results (3)

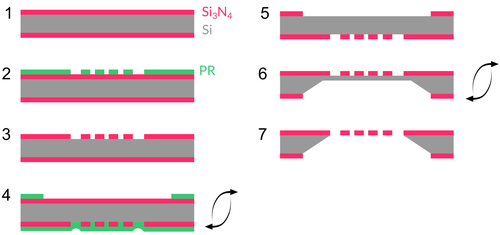

A fabrication method for large-area, high-stress LPCVD \mathrm{Si_3N_4} membranes is presented. These devices can be used as mechanical resonators with very low dissipation, exploiting dissipation dilution. A phononic crystal pattern allows to work with a high-order localized mode, shielded from acoustic radiation in the substrate. The procedure is amenable to most research clean rooms, requiring conventional lithography techniques and wet etching in KOH for device undercut.

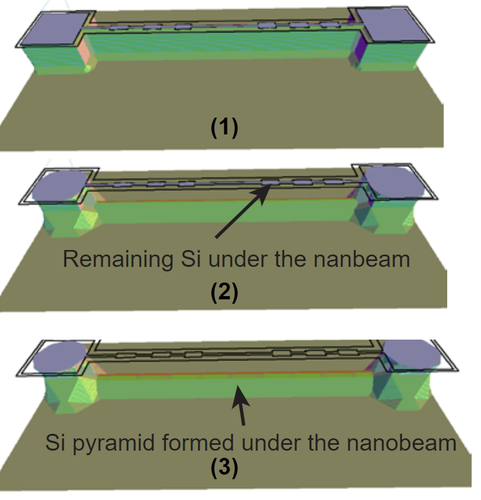

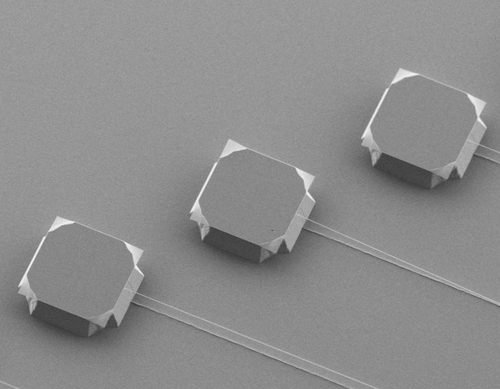

We describe the fabrication of high-stress Si_3N_4 nanobeam resonators with high aspect ratios exceeding lengths of 3.5mm. The lowest order out-of-plane modes of these nanobeams have quality factors of Q\geq 10^6 with fundamental mode frequencies lying in the range of 80-500kHz. The beams are fabricated from high-stress, 20-50nm-thick films of Si_3N_4 deposited via LPCVD on standard silicon wafers. The beams are patterned via electron beam lithography and deep reactive ion etching. The underlying silicon is ...

Results per page