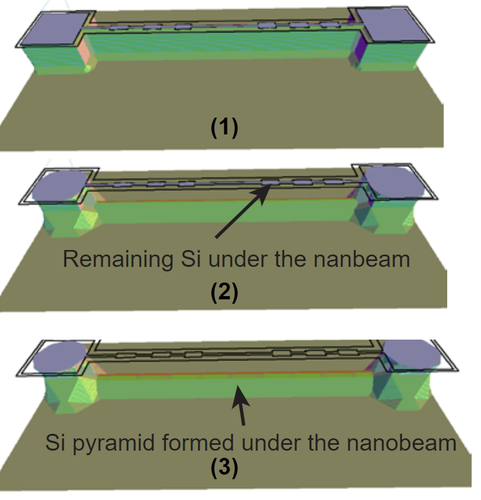

Here I explain the KOH simulator software (ACES) from University of Chicago [1] for a chain process of DRIE followed by KOH undercut. This software is very simple yet power to understand how Si etching works and design the mask to optimize the etch speed and crystal planes [2].

Results (5)

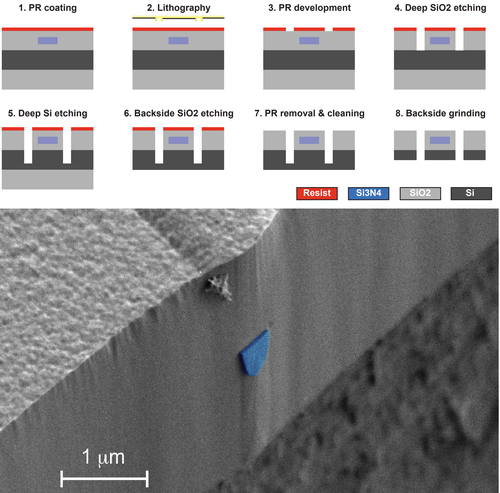

This short article describes a method to separate a wafer into photonic chips or dice, using dry etching and backside grinding. This method enables smooth chip facets that are advantageous for edge coupling with fibers or other chips.

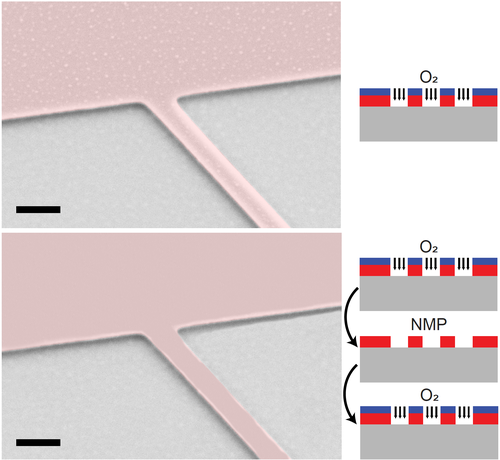

Resist removal is an essential step for multi-layer lithography processes where a clean and contamination-free surface is essential to avoid shadow etching patterns from resist leftovers. We show that a short \mathrm{O_2} plasma exposure followed by a full NMP solution cycle removes the resist fully and leaves the surface contamination free.

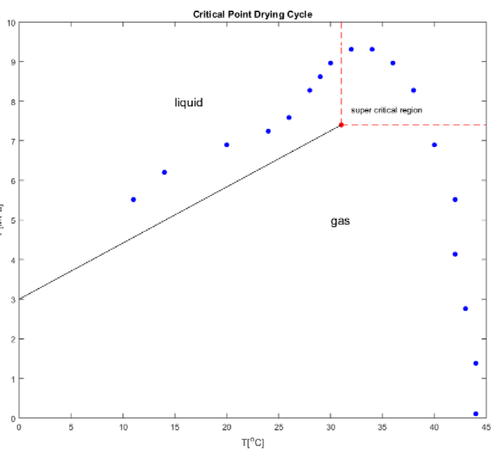

In this report I monitor a full successful cycle of critical point drying (CPD) run for drying MEMS sensors after wet release using KOH etching. The pressure and temperature of the CPD tool (Tousimis) is monitored during the process and plotted in a P-T diagram with \mathrm{CO_2} critical point. A few notes for higher yield in the drying process are mentioned in this report as well.

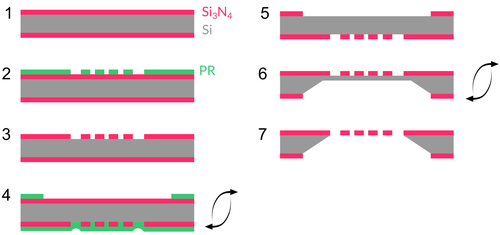

A fabrication method for large-area, high-stress LPCVD \mathrm{Si_3N_4} membranes is presented. These devices can be used as mechanical resonators with very low dissipation, exploiting dissipation dilution. A phononic crystal pattern allows to work with a high-order localized mode, shielded from acoustic radiation in the substrate. The procedure is amenable to most research clean rooms, requiring conventional lithography techniques and wet etching in KOH for device undercut.

Results per page